干货|射频电路设计要点

1、射频电路中元器件封装的注意事项

成功的RF设计必须仔细注意整个设计过程中每个步骤及每个细节,这意味着必须在设计开始阶段就要进行彻底的、仔细的规划,并对每个设计步骤的进展进行全面持续的评估。而这种细致的设计技巧正是国内大多数电子企业文化所欠缺的。

近几年来,由于蓝牙设备、无线局域网络(WLAN)设备,和移动电话的需求与成长,促使业者越来越关注RF电路设计的技巧。从过去到现在,RF电路板设计如同电磁干扰(EMI)问题一样,一直是工程师们最难掌控的部份,甚至是梦魇。若想要一次就设计成功,必须事先仔细规划和注重细节才能奏效。

射频(RF)电路板设计由于在理论上还有很多不确定性,因此常被形容为一种「黑色艺术」(black art) 。但这只是一种以偏盖全的观点,RF电路板设计还是有许多可以遵循的法则。不过,在实际设计时,真正实用的技巧是当这些法则因各种限制而无法实施时,如何对它们进行折衷处理。重要的RF设计课题包括:阻抗和阻抗匹配、绝缘层材料和层叠板、波长和谐波...等。

在 WiFi 产品的开发过程中,射频电路的布线(RF Circuit Layout Guide)是极为关键的一个过程。很多时候,我们可能在原理上已经设计的很完善,但是在实际的制板,上件过后发现很不理想,实际上这些都是布线(Layout)做的不够完善的原因。本文将以一个无线网卡的布线实例及本人的一点工作经验为大家讲解一下射频电路在布线中应该注意的一些问题。

在进行布线之前,我们首先要确定电路板的叠构,就像盖房子要先有房子的墙壁。电路板的叠构的确定与电路设计的复杂度,电磁兼容的考虑等很多因素有关。下图给出了四层板,六层板和八层板的常用叠构方式。

在无线网卡的PCB叠构中,基本上不会出现单面板的情况,所以本文也不会对单面板的情况加以讨论。两层板设计中应该注意的问题。

在四层板的设计中,我们一般会将第二层作为完整的地平面,同时,也会把重要的信号线走在顶层(当然包括射频走线),以便于很好的控制阻抗。在六层板或者更多层板的设计中,我们同样会将第二层作为完整的地平面,然后在顶层走最重要的信号线。

PS:可以使用Polar计算单端阻抗与阻抗等,有些Layout软件自身就集成了阻抗计算器,如Allegro。

在我们进行原理设计与仿真之后,在Layout中很值得注意的一件事情就是阻抗控制。众所周知,我们应该尽量保证走线的特征是50欧姆,这主要和线宽有关,在本实例中,是两层半,在Polar中采用Surface Coplanar Line模型进行阻抗的计算,我们可以得到一组比较理想的值:Height(H)=39.6mil,Track(W)=30mil,Track(W1)=30mil,Thickness=1OZ=1.4mil, Separation(S)=7mil, Dielectric(Er)=4.2,对应的特征阻抗是52.14欧姆,符合要求。如下图中高亮的线就是这样的一条射频走线。

射频元器件的摆放

相信做过射频设计的人都应该知道,我们应该尽可能的使走线的长度较短,元器件摆放的越紧凑越好(特殊要求除外),同时,也会尽可能的保证元器件的摆放对布线很有利(不要使走线绕来绕去的)。如下图,是射频功率放大器(PA,Power Amplifier)的周围器件的摆放,我们看到,元器件之间的距离很小。

射频走线应该注意的问题

如前所述,射频走线的长度要尽量短,线宽严格按照计算好的值去设定。在走线是尤其要注意的是,射频走线中不要有任何带有尖状的折点,在走线的转折处,最好要用弧线来实现,如下图

其次,在多层板的走线中,有可能重要的射频线要产生不可避免的交叉,这时我们就要使用我们最不想使用的东西:过孔。这样,会有部分射频信号线走到底层甚至中间层,但无论是哪一层,射频走线一定会有参考平面,这时一个值得注意的问题就是不要跨层,或者说不要使地平面不连续。

过孔的放置

过孔的放置真的是一件比较复杂的事情,本文只讨论那种接地的过孔。

首先,射频走线的旁边的地线最好能通过过孔打穿,接到底层或者中间层的地平面上,这样可以是任何干扰信号或者辐射有最短的到地的通路,但是,过孔与射频信号线的距离又不能太近,否则会严重影响射频信号质量,在实际的设计过程中可灵活把握,如下图,我们看到,高亮的信号线两层分布着很多过孔。

其次,在面积较大的地平面处,我们通常会放置很多的过孔用于连接不同层的地。这在射频电路的布线中,要注意的就是大过孔要没有规律的打,最好能弄成菱形的,这样可以最大限度的抑制各种干扰。

2、射频电路电源设计注意事项

(1)电源线是EMI 出入电路的重要途径。通过电源线,外界的干扰可以传入内部电路,影响RF电路指标。为了减少电磁辐射和耦合,要求DC-DC模块的一次侧、二次侧、负载侧环路面积最小。电源电路不管形式有多复杂,其大电流环路都要尽可能小。电源线和地线总是要很近放置。

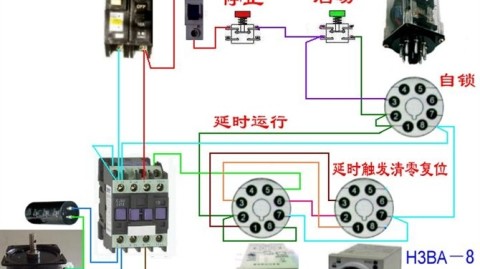

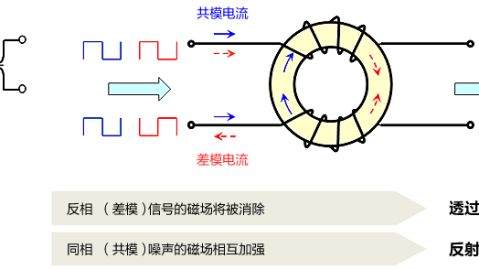

(2)如果电路中使用了开关电源,开关电源的外围器件布局要符合各功率回流路径最短的原则。滤波电容要靠近开关电源相关引脚。使用共模电感,靠近开关电源模块。

(3)单板上长距离的电源线不能同时接近或穿过级联放大器(增益大于45dB)的输出和输入端附近。避免电源线成为RF信号传输途径,可能引起自激或降低扇区隔离度。长距离电源线的两端都需要加上高频滤波电容,甚至中间也加高频滤波电容。

(4)RF PCB的电源入口处组合并联三个滤波电容,利用这三种电容的各自优点分别滤除电源线上的低、中、高频。例如:10uf,0.1uf,100pf。并且按照从大到小的顺序依次靠近电源的输入管脚。

(5)用同一组电源给小信号级联放大器馈电,应当先从末级开始,依次向前级供电,使末级电路产生的EMI 对前级的影响较小。且每一级的电源滤波至少有两个电容:0.1uf,100pf。当信号频率高于1GHz时,要增加10pf滤波电容。

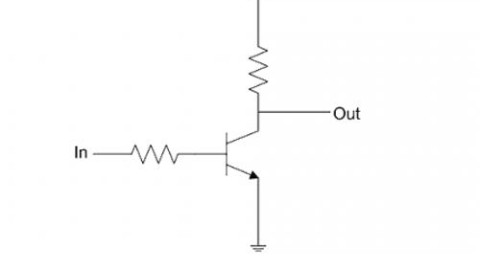

(6)常用到小功率电子滤波器,滤波电容要靠近三极管管脚,高频滤波电容更靠近管脚。三极管选用截止频率较低的。如果电子滤波器中的三极管是高频管,工作在放大区,外围器件布局又不合理,在电源输出端很容易产生高频振荡。线性稳压模块也可能存在同样的问题,原因是芯片内存在反馈回路,且内部三极管工作在放大区。在布局时要求高频滤波电容靠近管脚,减小分布电感,破坏振荡条件。

(7)PCB的POWER部分的铜箔尺寸符合其流过的最大电流,并考虑余量(一般参考为1A/mm线宽)。

(8)电源线的输入输出不能交叉。

(9)注意电源退耦、滤波,防止不同单元通过电源线产生干扰,电源布线时电源线之间应相互隔离。电源线与其它强干扰线(如CLK)用地线隔离。

(10)小信号放大器的电源布线需要地铜皮及接地过孔隔离,避免其它EMI干扰窜入,进而恶化本级信号质量。

(11)不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

(12)PCB板层分配便于简化后续的布线处理,对于一个四层PCB板(WLAN中常用的电路板),在大多数应用中用电路板的顶层放置元器件和RF引线,第二层作为系统地,电源部分放置在第三层,任何信号线都可以分布在第四层。

第二层采用连续的地平面布局对于建立阻抗受控的RF信号通路非常必要,它还便于获得尽可能短的地环路,为第一层和第三层提供高度的电气隔离,使得两层之间的耦合最小。当然,也可以采用其它板层定义的方式(特别是在电路板具有不同的层数时),但上述结构是经过验证的一个成功范例。

(13)大面积的电源层能够使Vcc布线变得轻松,但是,这种结构常常是引发系统性能恶化的导火索,在一个较大平面上把所有电源引线接在一起将无法避免引脚之间的噪声传输。反之,如果使用星型拓扑则会减轻不同电源引脚之间的耦合。

上图给出了星型连接的Vcc布线方案,该图取自MAX2826 IEEE 802.11a/g收发器的评估板。图中建立了一个主Vcc节点,从该点引出不同分支的电源线,为RF IC的电源引脚供电。每个电源引脚使用独立的引线在引脚之间提供了空间上的隔离,有利于减小它们之间的耦合。另外,每条引线还具有一定的寄生电感,这恰好是我们所希望的,它有助于滤除电源线上的高频噪声。

使用星型拓扑Vcc引线时,还有必要采取适当的电源去耦,而去耦电容存在一定的寄生电感。事实上,电容等效为一个串联的RLC电路,电容在低频段起主导作用,但在自激振荡频率(SRF):

之后,电容的阻抗将呈现出电感性。由此可见,电容器只是在频率接近或低于其SRF时才具有去耦作用,在这些频点电容表现为低阻。

给出了不同容值下的典型S11参数,从这些曲线可以清楚地看到SRF,还可以看出电容越大,在较低频率处所提供的去耦性能越好(所呈现的阻抗越低)。

在Vcc星型拓扑的主节点处最好放置一个大容量的电容器,如2.2μF。该电容具有较低的SRF,对于消除低频噪声、建立稳定的直流电压很有效。IC的每个电源引脚需要一个低容量的电容器(如10nF),用来滤除可能耦合到电源线上的高频噪声。对于那些为噪声敏感电路供电的电源引脚,可能需要外接两个旁路电容。例如:用一个10pF电容与一个10nF电容并联提供旁路,可以提供更宽频率范围的去耦,尽量消除噪声对电源电压的影响。每个电源引脚都需要认真检验,以确定需要多大的去耦电容以及实际电路在哪些频点容易受到噪声的干扰。

良好的电源去耦技术与严谨的PCB布局、Vcc引线(星型拓扑)相结合,能够为任何RF系统设计奠定稳固的基础。尽管实际设计中还会存在降低系统性能指标的其它因素,但是,拥有一个“无噪声”的电源是优化系统性能的基本要素.

3、射频PCB设计的EMC规范

1 层分布

1.1 双面板,顶层为信号层,底面为地平面。

1.2 四层板,顶层为信号层,第二层为地平面,第三层走电源、控制线。特殊情况下(如 射频信号线要穿过屏蔽壁),在第三层要走一些射频信号线。每层均要求大面积敷地。

1.2 四层板,顶层为信号层,第二层为地平面,第三层走电源、控制线。特殊情况下(如 射频信号线要穿过屏蔽壁),在第三层要走一些射频信号线。每层均要求大面积敷地。

2 接地

2.1 大面积接地 为减少地平面的阻抗,达到良好的接地效果,建议遵守以下要求:a) 射频 PCB 的接地要求大面积接地;b) 在微带印制电路中,底面为接地面,必须确保光滑平整;c) 要将地的接触面镀金或镀银,导电良好,以降低地线最抗;d) 使用紧固螺钉,使其与屏蔽腔体紧密结合,紧固螺钉的间距小于λ/20(依具体情 况而定)。

2.2 分组就近接地 按照电路的结构分布和电流的大小将整个电路分为成相对独立的几组,各组电路就 近接地形成回路,要调整各组内高频滤波电容方向,缩小电源回路。注意接地线要短而直, 禁止交叉重叠,减少公共地阻抗所产生的干扰。

2.3 射频器件的接地 表面贴射频器件和滤波电容需要接地时,为减少器件接地电感,要求:a) 至少要有 2 根线接铺地铜箔;b) 用至少 2 个金属化过孔在器件管脚旁就近接地。c) 增大过孔孔径和并联若干过孔。d) 有些元件的底部是接地的金属壳,要在元件的投影区内加一些接地孔,表面层 不得布线。

2.4 微带电路的接地 微带印制电路的终端单一接地孔直径必须大于微带线宽,或采用终端大量成排密布小孔 的方式接地。

2.5 接地工艺性要求

a) 在工艺允许的前提下,可缩短焊盘与过孔之间的距离;

b) 在工艺允许的前提下,接地的大焊盘可直接盖在至少 6 个接地过孔上(具体数量因 焊盘大小而异);

c) 接地线需要走一定的距离时,应缩短走线长度,禁止超过λ/20,以防止天线效应 导致信号辐射;

d) 除特殊用途外,不得有孤立铜箔,铜箔上一定要加地线过孔;

e) 禁止地线铜箔上伸出终端开路的线头。

3 屏蔽

3.1 射频信号可以在空气介质中辐射。空间距离越大,工作频率越低,输入输出端的寄 生耦合就越小,隔离度则越大。PCB 典型的空间隔离度约为 50dB。

3.2 敏感电路和强烈辐射源电路要加屏蔽,但如果设计加工有难度时(如空间或成本限 制等),可不加,但要做试验最终决定。这些电路有:

a) 接收电路前端是敏感电路,信号很小,要采用屏蔽。

b) 对射频单元和中频单元须加屏蔽。接收通道中频信号会对射频信号产生较大干扰, 反之,发射通道的射频信号对中频信号也会造成辐射干扰。

c) 振荡电路:强烈辐射源,对本振源要单独屏蔽,由于本振电平较高,对其他单元形 成较大的辐射干扰。

d) 功放及天馈电路:强烈辐射源,信号很强,要屏蔽。

e) 数字信号处理电路:强烈辐射源,高速数字信号的陡峭的上下沿会对模拟的射频信 号产生干扰。

f) 级联放大电路:总增益可能会超过输出到输入端的空间隔离度,这样就满足了振荡 条件之一,电路可能自激。如果腔体内的电路同频增益超过 30-50dB,必须在 PCB 板 上焊接或安装金属屏蔽板,增加隔离度。实际设计时要综合考虑频率、功率、增益情况 决定是否加屏蔽板。

g) 级联的滤波、开关、衰减电路:在同一个屏蔽腔内,级联滤波电路的带外衰减、级 联开关电路的隔离度、级联衰减电路的衰减量必须小于 30-50dB。如果超过这个值, 必须在 PCB 板上焊接或安装金属屏蔽板,增加隔离度。实际设计时要综合考虑频率、功 率、增益情况决定是否加屏蔽板。

h) 收发单元混排时应屏蔽。

i) 数模混排时,对时钟线要包地铜皮隔离或屏蔽。

4 屏蔽材料和方法

4.1 常用的屏蔽材料均为高导电性能材料,如铜板、铜箔、铝板、铝箔。钢板或金属镀 层、导电涂层等。

4.2 静电屏蔽主要用于防止静电场和恒定磁场的影响。应注意两个基本要点,即完善的 屏蔽体和良好的接地性。

4.3 电磁屏蔽主要用于防止交变磁场或交变电磁场的影响,要求屏蔽体具有良好的导电 连续性,屏蔽体必须与电路接在共同的地参考平面上,要求 PCB 中屏蔽地与被屏蔽电路地要 尽量的接近。

4.4 对某些敏感电路,有强烈辐射源的电路可以设计一个在 PCB 上焊接的屏蔽腔,PCB 在 设计时要加上“过孔屏蔽墙”,就是在 PCB 上与屏蔽腔壁紧贴的部位加上接地的过孔。要求 如下:

a) 有两排以上的过孔;

b) 两排过孔相互错开;

c) 同一排的过孔间距要小于λ/20;

d) 接地的 PCB 铜箔与屏蔽腔壁压接的部位禁止有阻焊。

4.5 射频信号线在顶层穿过屏蔽壁时,要在屏蔽腔相应位置开一个槽门,门高大于 0.5mm, 门宽要保证安装屏蔽壁后信号线与屏蔽体间的距离大于 1mm。

5 屏蔽罩设计

5.1 金属屏蔽腔的基本结构

5.1.1 此类屏蔽罩被广泛使用,如图 27。材料一般为薄的铝合金,制造工艺一般采用冲 压折弯或压力铸造工艺,这种屏蔽罩有较多的螺钉孔,便于螺钉固定。部分需铝合金盖子和 吸波材料增强屏蔽性能。射频 PCB 需装在屏蔽腔内,要选择合适的屏蔽腔尺寸,使其最低 谐振频率远高于工作频率,最好 10 倍以上,详见附录 G“金属屏蔽腔的尺寸设计”。

5.1.2 屏蔽腔的高度一般为第一层介质厚度 15-20 倍或以上,在屏蔽腔面积一定时,要 提高屏蔽腔的最低谐振频率,需增加长宽比,避免正方形的腔体,如图 。

5.2 金属屏蔽腔对 PCB 布局的工艺要求

5.2.1 屏蔽罩与 PCB 板接触的罩体设计时应考虑 PCB bottom 面的器件高度,特别是插 件器件引脚伸出的高度。

5.2.2 需考虑螺丝禁布区的大小,防止组装时损坏表层线路或器件。射频功放板由于结 构尺寸的限制,其单板尺寸相对较小,故一般要求螺钉安装空间(禁布区)至少在安装孔焊 盘外侧。螺钉安装空间见表 5

.5.2.3 金属屏蔽罩自身成本和装配成本很贵,并且外形不规则的金属屏蔽罩在制造时很 难保证高精度和高平整性,又使元器件布局受到一些限制;金属屏蔽罩不利于元器件更换和 故障定位。

5.2.4 尽可能保证屏蔽罩的完整非常重要,进入金属屏蔽罩的数字信号线应该尽可能走 内层,RF 信号线可以从金属屏蔽罩底部的小缺口和地缺口处的布线层上走出去,不过缺口 处周围要尽可能地多布一些地,不同层上的地可通过多个过孔连在一起。

5.2.5 为保证装配和返修,金属屏蔽罩周围5mm范围内不能有超过其高度的器件,Chip 小器件到屏蔽罩的距离应该2mm以上,其它器件距离要求3mm以上,并且放置朝向最好 符合方便维修方向。

5.2.6 金属屏蔽罩内部不能有超过其高度的器件,并且器件顶部到屏蔽罩面的距离要符 合安全规范要求。

5.2.7 需考虑 SMA 微带插座与 PCB 板接触时的高度匹配,否则焊接可靠性存在影响。如图29所示,设计时须考虑PCB板厚的公差(±10%),金属屏蔽腔的加工误差(±0.05mm)。建议 SMA 微带插座与 PCB 板的高度间隙不超过 0.5mm,插座与焊盘不允许有明显偏差。

5.2.8 由于功放板设计的特殊情况,容许 2 块单板之间信号穿过屏蔽罩,并用飞线连接, 如图

4、射频走线与地

举个例子来说吧。我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的PCB文件如下图1所示(两种线宽):

图1a:线宽0.1016 mm的射频线(表层铺地前)

图1b:线宽0.35 mm的射频线(表层铺地前)

首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

图2a:表层未铺地的S21 (线宽0.1016mm)

图2b:表层未铺地的S21 (线宽0.35mm)

由图中可以看到,在800MHz-1GHz的范围内,仿真的数据展示为小数点后一到两位的数量级,0.35mm的损耗要比0.1016mm的线小一个数量 级,这是因为0.35mm的线宽在该板的层叠条件下其特征阻抗接近50Ω。因此间接验证了我们所做的阻抗计算(用线宽约束)是有一定作用的。

接下来我们做了表层铺地后的同样的仿真(800MHz-1GHz),导入的PCB文件如下图。

图3a:0.1016 mm的射频线(表层铺地)

图3b:0.35 mm的射频线(表层铺地)

图3:表层铺过地后的PCB

仿真结果如下图:

图4a:表层铺地后的S21 (0.1016mm)

图4b:表层铺地后的S21 (0.35mm)

图4:表层铺过地后的S21

由图中看到,仿真的数据显示,该传输线的线损已经是1-2 dB的数量级了,当然0.35 mm的损耗要明显小于0.1016 mm的。另外一个明显的现象是相对于未铺地的仿真结果,随着频率由800MHz到1GHz的增加,损耗趋大。

我们可以从仿真的结果中得到这样一个结果:

1.射频走线最好按50欧姆走,可以减小线损; 2.表层的铺地事实上是将一部分RF信号能量耦合到了地上,造成了一定的损耗。 因此PCB表层的铺地应该有所讲究。尽量远离RF线。工程经验是大于1.5倍的线宽。

【5】设计checklist

大类 小类 编号 要素描述 通用 布局1

ESD防护元件直接放在主信号路径上。

2

模块分腔屏蔽合理,己关注腔体自谐振频率。

3

屏蔽墙及内倒角位置的顶面是布局、布线、信号过孔禁布区。

4

匹配元件靠近相关的RF器件端口布局

5

已考虑热设计,保证热量不集中,散热容易。

6

RF主信号流一字布局,如果受空间限制,不能一字布局时,可以采用L形布局,慎用U形布局。

7

对绕线电感的布局必须要保证相邻电感的磁力线相互垂直,对印制线类电感(LTCC工艺)如做不到磁力线相互垂直,应该远离放置。

8

分立元件构成的组合电路,不被其它元件或传输线打散,例如电阻衰减器的三个电阻布局互相靠近。滤波器电路要一面布局,并且不能被其它传输线打散。

9

高中低频组合滤波,高频小容量滤波电容最靠近器件管脚。

10

PCB螺钉数量和布局合理。

11

功放PCB开窗综合考虑了安装余量和电气性能。

12

功放可变电容、隔直电容位置己按原理图设计者要求布局。

13

元件离屏蔽壁间距符合要求,考虑了误差。

14

射频PCB的输入输出和其它部分的接口是否满足设计要求。

15

在正常工作或测试环境下,没有Stub。

17

数字芯片PWM调制输出直流的RC滤波电路,放置在数字芯片侧。

18

腔内同频增益超过40dB级联放大电路需进行了分腔。例如:接收通道的增益一般会很大,需要进行分腔

19

级联衰减电路的衰减量大于40dB的电路需进行分腔。

20

级联滤波电路的带外衰减和级联开关电路的隔离度大于40dB,则需要分腔。

21

射频电源的分配一般按照就近供电的原则,以免相互之间产生干扰。同时,在不同芯片共用同一个电源芯片时,要注意芯片之间是否会通过电源产生干扰。

22

电源的摆放位置是否合适,要保证输入输出电源线不能交叉,走线距离最短。

23

电源输入口的滤波电容是否靠近输入管脚,并且按照从大到小的顺序排列,容值最小的电容最靠近电源的输入管脚。

24

器件DATASHEET上有特殊要求的布局是否满足。

布线1

布RF线需要进行控制走线阻抗,将它们布得尽可能直接,这样可以减小损耗和不期望得到的耦合。

2

微带线下方需要连续的地,同样的,带状线上方和下方也需要连续的地;地平面不仅提供需要的回路,还可以将信号跟其它信号层隔离;

3

长的、没有屏蔽的走线,如RF前端的连线需要用带状线,这样有利于使用固有的屏蔽。

4

避免在内层和外层多次来回走线;

5

当RF信号线在不同层之间过渡时,过孔需要远离潜在的干扰电路、走线及过孔(比如数字控制线、时钟、电源等);确保射频过孔和干扰路径之间铺地并加地过孔,起隔离作用。

6

时钟线、数据线、控制线之间的距离需满足3W原则。如果空间允许,尽量拉开线间距离。

7

走线要最短,不能闭环,不能有锐角和直角。

8

晶振表面以下不能有过孔和走线。频综、pll滤波器件、VCO、滤波器和电感下表面不能走线。

9

模拟信号与数字信号,电源线与控制信号线,弱信号与其他任何信号需要分层(最好有地隔离)或相距较远走线。如果分层相邻层的线与线之间不能并行走线,最好垂直走线。如果没有分层线间的距离是要满足隔离度的要求,至少满足线距大于3W。

10

射频敏感信号不能靠近强辐射信号。

11

差分信号线需对称走线,线长相差不能超过100mil,差分线对间的间距需满足3W规则。

12

输入输出阻抗不是50欧姆的器件,输入输出阻抗线需满足阻抗匹配要求。

13

在原理图中,有特殊要求的阻抗线需满足原理图的设计要求。

14

不同单元电源线布线时,电源线之间需相互隔离,以免各单元电路通过电源相互干扰。

15

不同电源层在空间上不能重叠,如果重叠需要有地层隔离。

16

电源的走线线宽要满足电流的通流量要求。(一般参考为1A/mm线宽)

17

RF信号布线周围如果存在其它RF信号线,在两者之间需辅地铜皮,并打地过孔。

18

电源部分导线印制线在层间转接的过孔数符合通过电流的要求(1A/Ф0.3mm孔)。

19

RF信号布线周围如果存在其它不相关的非RF信号(如过路电源线),在两者之间需辅地铜皮,并打地过孔。

20

小信号放大器的电源布线需要地铜皮及接地过孔隔离,避免其它EMI干扰窜入,进而恶化本级信号质量。

21

接地线要短而直,减少分布电感,减小公共地阻抗所产生的干扰。

22

RF 主信号路径上的接地器件和电源滤波电容需要接地时,为减小器件接地电感,要求就近接地。

23

有些元件的底部是接地的金属壳,要在元件的投影区内加一些接地孔,投影区内的表面层不得布信号线和过孔;

24

接地线需要走一定的距离时,应加粗走线线宽、缩短走线长度,禁止接近和超过1/4导引波长,以防止天线效应导致信号辐射;

25

除特殊用途外,不得有孤立铜皮,铜皮上一定要加地线过孔。

26

对某些敏感电路、有强烈辐射源的电路分别放在屏蔽腔内,装配时屏蔽腔压在PCB表面。PCB在设计时要加上“过孔屏蔽墙”,就是在PCB上与屏蔽腔壁紧贴的部位加上接地的过孔。要有两排以上的过孔,两排过孔相互错开,同一排的过孔间距在100mils左右。

27

一些RF器件封装较小,SMD焊盘宽度可能小至12mils,而RF信号线宽可能达50mils以上,要用渐变线,禁止线宽突变,且过渡部分的线不宜太长。

28

当50欧细微带线上有大焊盘时,大焊盘相当于分布电容,破坏了微带线的特性阻抗连续性。需将焊盘下方的地平面挖空,来减小焊盘的分布电容。并通过软件仿真,保证阻抗为50欧姆。

29

过孔是引起RF 通道上阻抗不连续性的重要因素之一,如果信号频率大于1GHz,就要考虑过孔的影响。具体情况需用HFSS和Optimetrics进行优化仿真。

射频模块 频率源模块1

数据、时钟、使能线不能在数字频率合成器芯片、晶体、晶振、变压器、光耦、电源模块等器件底部表面层走线。

2

频综的电源线要和其他干扰信号进行隔离,以免影响频综的相位噪声和杂散。

3

环路滤波器的布局要同层布局,并且结构紧凑,靠近相关的滤波管脚,在滤波器的下表面不能走线。

4

VCO的电源和控制电压,要和其它干扰信号进行隔离。

5

VCO和频综下面不能走线。

6

频综的数据、时钟、使能信号之间的距离要满足至少3W的间距。如果分层布线,不能平行重叠走线。

参考源模块1

参考源的参考输入信号,是从中频送过来的,走线一定要短,不能对其它电路有影响。

2

数据、时钟、使能信号之间的距离要满足至少3W的间距。如果分层布线,不能平行重叠走线。

4

VCO的电源和控制电压,要和其它干扰信号进行隔离。

5

参考源的输出电路要和其它信号进行隔离。

LNA 模块1

LNA的输入信号线要越短越好。减小线损,增强接收通道的灵敏度。

2

LNA的匹配电路要靠近相应的管脚放置。

3

射频前端的ESD防护电路,一定要放在射频信号的主干线上,以防降低防护等级。

小信号放大器模块1

小信号放大器的电源布线需要地铜皮及接地过孔隔离,避免其它EMI干扰窜入,进而恶化本级信号质量。

2

单片放大器偏置电感的焊盘也最好放在RF信号线上,如果空间紧张也可通过12mil高阻线与RF信号线相连 。

3

当同一电源给两级放大器同时供电时,电源要从后级向前级供电,以免末级放大电路影响前级。

4

小信号放大器的电源地回路要小,电容接地要短而直,减小公共地阻抗所产生的干扰。

滤波器模块1

滤波器的匹配元件要靠近相应的管脚。

2

当滤波器的输入输出管脚为大焊盘时,为了保证阻抗的连续性,需要将其下面的层挖空。需通过仿真软件计算具体的阻抗值。

3

当滤波器底部是金属外壳与接地脚相连,器件的元件面投影区是禁布区,不能布微带线和过孔,

集成混频器1

要注意混频器的外围器件应该按照DATASHEET的要求布局。

2

对于集成双平衡混频器,扼流电感和隔离电感一定要远离,并且垂直放置。

3

对于集成双平衡混频器,隔离电感的接地必须充分,尽量在附近多打地孔。

4

对于集成双平衡混频器,两个扼流电感要保持对称平行放置

集成调制器1

I/Q是两对差分线对,这两对差分线对间的间距满足3W规则,并且中间要加地孔隔离。

2

I/Q分别是两对差分线对,这两对差分线要并行走线,不能交叉走线。

3

两对差分线线长相差不能超过100mil。

4

差分线走线过孔不能超过4个。

电源电路 射频电源1

电源线是EMI 出入电路的重要途径。通过电源线,外界的干扰可以传入内部电路,影响RF电路指标。为了减少电磁辐射和耦合,要求DC-DC模块的一次侧、二次侧、负载侧环路面积最小。电源电路不管形式有多复杂,其大电流环路都要尽可能小。

2

单板上长距离的电源线不能同时接近或穿过级联放大器(增益大于45dB)的输出和输入端附近。避免电源线成为RF 信号传输途径,可能引起自激或降低扇区隔离度。长距离电源线的两端都需要加上高频滤波电容,甚至中间也加高频滤波电容。

3

RF PCB的电源入口处组合并联三个滤波电容,利用这三种电容的各自优点分别滤除电源线上的低、中、高频。例如:10uf,0.1uf,100pf。并且按照从大到小的顺序依次靠近电源的输入管脚。

4

用同一组电源给小信号级联放大器馈电,应当先从末级开始,依次向前级供电,使末级电路产生的EMI 对前级的影响较小。且每一级的电源滤波至少有两个电容:0.1uf,100pf。当信号频率高于1GHz时,要增加10pf滤波电容。

5

不同电源层在空间上要避免重叠。主要是为了减少不同电源之间的干扰,特别是一些电压相差很大的电源之间,电源平面的重叠问题一定要设法避免,难以避免时可考虑中间隔地层。

6

电源部分导线印制线在层间转接的过孔数符合通过电流的要求(1A/Ф0.3mm孔)。

7

PCB的POWER部分的铜箔尺寸符合其流过的最大电流,并考虑余量(一般参考为1A/mm线宽)。

8

电源线的输入输出不能交叉。

其它 安规1

电源印制导线在层间转接的过孔数符合通过电流的要求(1A/Ф0.3孔)

2

PCB的POWER部分的铜箔尺寸符合其流过的最大电流,并考虑余量(一般参考为2A/mm线宽)

3

单板上高温元器件的防护和热处理措施合理(类似加热器件的高温元器件处理)

4

较大面积可触及导电零部件外壳与地连接(如DC/DC外壳、屏蔽盒)

5

较大体积零件的固定孔及安装后的电气间隙和在印制板上的爬电距离符合安规要求。(如DC/DC外壳、屏蔽盒)

6

屏蔽盒固定后,与其它接插件等带能量危险或与危险电压电极的电气间隙达到安规要求;固定螺钉及垫片在印制板上爬电距离符合要求。

7

-48V输入印制线位于重叠位置,层间距离没有小于0.1mm。

8

PCB电源部分的连接器有防止反插措施

9

DC/DC的输入/输出印制线,不与DC/DC模块在同一面(贴装DC/DC除外,无台阶的DC/DC外壳会与印制线的电气间隙不够,甚至会依靠阻焊剂绝缘)

10

功放输出口有保护电路(如环行器等)保证不会过功率引发过热或燃烧事件

11

防雷击连接器与气体放电管及保护二极管之间的布线要尽量粗,并且其布线到地的距离要大于80mil以上。

一、布局注意事项

(1) 结构设计要求 在 PCB 布局之前需要弄清楚产品的结构。

结构需要在 PCB 板上体现出来。比如腔壳的外边厚度大小,中间隔腔的厚度大小, 倒角半径大小和隔腔上的螺钉大小等等(换句话说,结构设计是根据 完成后的 PCB 上所画的轮廓(结构部分)进行具体设计的)。一般情 况,外边腔厚度为 4mm;内腔宽度为 3mm;点胶工艺的为 2mm;倒角 半径 2.5mm。以 PCB 板的左下角为原点,隔腔需在栅格 0.5 的整数倍, 最少需要做到栅格为 0.1 的整数倍。这样有利于结构加工商进行加工, 误差控制比较精确些。当然,这需要根据客户的要求来设计。

下图所示为 PCB 设计完成后的结构轮廓图:

(2) 布局要求 布局优先对射频链路进行布局,然后对其它电路进行布局。A 射频链路布局注意事项 完全根据原理图的先后顺序(输入到输出,包括每个元件的先后 位置和元件与元件之间的间距都有讲究的。有的元件与元件之间距离 不宜过大,比如π 网。)进行布局,布局成“一”字形或者“L”形。在实际的射频链路布局中,因受产品的空间限制,不可能完全实 现,这就迫使我们将布局成“U”形。布局成 U 形并不是不可以,但 需要在中间加隔腔将其左右进行隔离,做好屏蔽。

还有一种在横向也需要添加隔腔。即,用隔腔把一字形左右进行 隔离。这主要是因为需要隔离部分非常敏感或易干扰其它电路;另外, 还有一种可能就是一字形输入端到输出端这段电路的增益过大,也需 要用隔腔将其分开(若增益过大,腔体太大,可能会引起自激。)。

B 芯片外围电路布局 射频器件外围电路布局严格参照 datasheet 上面的要求进行布 局,受空间限制可以进行调整;数字芯片外围电路布局就不多讲了。

二、 布线注意事项

根据 50 欧姆阻抗线宽进行布线,尽量从焊盘中心出线,线成直 线,尽量走在表层。在需要拐弯的地方做成 45 度角或圆弧走线,推 荐在电容或电阻两边进行拐弯。如果遇到器件走线匹配要求的,请严 格按照 datasheet 上面的参考值长度走线。比如,一个放大管与电容 之间的走线长度(或电感之间的走线长度)要求等等。

在进行 PCB 设计时,为了使高频电路板的设计更合理,抗干扰性能更 好,应从以下几方面考虑(通用做法):

(1) 合理选择层数 在 PCB 设计中对高频电路板布线时,利用中间内层平面作为电源和 地线层,可以起到屏蔽的作用,有效降低寄生电感、缩短信号线长度、 降低信号间的交叉干扰。

(2) 走线方式 走线必须按照 45°角拐弯或圆弧拐弯,这样可以减小高频信 号的发射和相互之间的耦合。

(3) 走线长度 走线长度越短越好,两根线并行距离越短越好。

(4) 过孔数量 过孔数量越少越好。

(5) 层间布线方向 层间布线方向应该取垂直方向,就是顶层为水平方向,底层为 垂直方向,这样可以减小信号间的干扰。

(6) 敷铜 增加接地的敷铜可以减小信号间的干扰。

(7) 包地 对重要的信号线进行包地处理,可以显著提高该信号的抗干扰 能力,当然还可以对干扰源进行包地处理,使其不能干扰其他 信号。

(8) 信号线 信号走线不能环路,需要按照菊花链方式布线。

三、 接地处理

(1)射频链路接地 射频部分采用多点接地方式进行接地处理。射频链路铺铜间隙一般 30mil 到 40mil 用的比较多。两边都需要打接地孔,且间距尽量保持 一致。射频通路上对地电容电阻的接地焊盘,尽量就近打接地孔。器 件上的接地焊盘都需要打接地过孔。

(2)腔壳接地孔 为了让腔壳与 PCB 板之间更好的接触。一般打两排接地孔且交错方 式放置,如图 06 所示。PCB 隔腔上需要开窗,如图 07 所示。PCB 底 层接地铜皮与底板接触的地方都需要开窗处理,使其更好的接触。如 图 08 所示(PCB 板的上半部分与底座接触):

PCB 隔腔接地过孔图

PCB 隔腔开窗图

PCB 底层开窗图

(3)螺钉放置(需要了解结构知识) 为了使 PCB 与底座和腔壳之间有更紧密的接触(更好的屏蔽) 需要在 PCB 板上放置螺钉孔位置。PCB 与腔壳之间螺钉放置方法:隔腔每个交叉的地方放置一个螺 钉。在实际设计中,比较难实现,可以根据模块电路功能进行适当调 整。但不管怎样,腔壳四个角上必须都有螺钉。

腔壳螺钉图

PCB 与底座之间的螺钉放置方法:腔壳中的每个小腔内都需要有 螺钉,视腔大小而定螺钉数量(腔越大,放置的螺钉就多)。一般原 则是在腔的对角上放置螺钉。SMA 头或其他连接器旁边必须放置螺钉。在 SMA 头或连接器在插拔过程中不致 PCB 板变形。

腔内螺钉图

免责声明:本文系网络转载,版权归原作者所有。如本文所用视频、图片、文字如涉及作品版权问题,请在文末留言告知,我们将在第一时间处理!本文内容为原作者观点,并不代表本公众号赞同其观点和对其真实性负责。

干货 | 深度解析电源原理图和每个元件的功能

干货 | 九种常见的元器件封装技术

Wi-Fi产品射频电路调试经验谈

Wi-Fi产品射频电路调试经验谈

1 前言

这份文档总结了我工作一年半以来的一些射频(Radio Frequency)调试(以下称为Debug)经验,记录的是我在实际项目开发中遇到并解决问题的过程。现在我想利用这份文档与大家分享这些经验,如果这份文档能够对大家的工作起到一定的帮助作用,那将是我最大的荣幸。

个人感觉,Debug过程用的都是最简单的基础知识,如果能够对RF的基础知识有极为深刻(注意,是极为深刻)的理解,我相信,所有的Bug解起来都会易如反掌。同样,我的这篇文档也将会以最通俗易懂的语言,讲述最通俗易懂的Debug技巧。

在本文中,我尽量避免写一些空洞的理论知识,但是第二章的内容除外。“微波频率下的无源器件”这部分的内容截取自我尚未完成的“长篇大论”——Wi-Fi产品的一般射频电路设计(第二版)。

我相信这份文档有且不只有一处错误,如果能够被大家发现,希望能够提出,这样我们就能够共同进步。

2 微波频率下的无源器件

在这一章中,主要讲解微波频率下的无源器件。一个简单的问题:一个1K的电阻在直流情况下的阻值是1K,在频率为10MHz的回路中可能还是1K,但是在10GHz的情况下呢?它的阻值还会是1K吗?答案是否定的。在微波频率下,我们需要用另外一种眼光来看待无源器件。

2.1. 微波频率下的导线

微波频率下的导线可以有很多种存在方式,可以是微带线,可以是带状线,可以是同轴电缆,可以是元件的引脚等等。

2.1.1. 趋肤效应

在低频情况下,导线内部的电流是均匀的,但是在微波频率下,导线内部会产生很强的磁场,这种磁场迫使电子向导体的边缘聚集,从而使电流只在导线的表面流动,这种现象就称为趋肤效应。趋肤效应导致导线的电阻增大,结果会怎样?当信号沿导体传输时衰减会很严重。

在实际的高频场合,如收音机的感应线圈,为了减少趋肤效应造成的信号衰减,通常会使用多股导线并排绕线,而不会使用单根的导线。

我们通常用趋肤深度来描述趋肤效应。趋肤深度是频率与导线本身共同的作用,在这里我们不会作深入的讨论。

2.1.2. 直线电感

我们知道,在有电流流过的导线周围会产生磁场,如果导线中的电流是交变电流,那么磁场强度也会随着电流的变化而变化,因此,在导线两端会产生一个阻止电流变化的电压,这种现象称之为自感。也就是说,微波频率下的导线会呈现出电感的特性,这种电感称为直线电感。也许你会直线电感很微小,可以忽略,但是我们将会在后面的内容中看到,随着频率的增高,直线电感就越来越重要。

电感的概念是非常重要的,因为微波频率下,任何导线(或者导体)都会呈现出一定的电感特性,就连电阻,电容的引脚也不例外。

2.2. 微波频率下的电阻

从根本上说,电阻是描述某种材料阻碍电流流动的特性,电阻与电流,电压的关系在欧姆定律中已经给出。但是,在微波频率下,我们就不能用欧姆定律去简单描述电阻,这个时候,电阻的特性应经发生了很大的变化。

2.2.1. 电阻的等效电路

电阻的等效电路如图2-1所示。其中R就是电阻在直流情况下电阻自身的阻值,L是电阻的引脚,C因电阻结构的不同而不同。我们很容易就可以想到,在不同的频率下,同一个电阻会呈现出不同的阻值。想想平时在我们进行Wi-Fi产品的设计,几乎不用到直插的元件(大容量电解电容除外),一方面是为了减小体积,另一方面,也是更为重要的原因,减小元件引脚引起的电感。

图2-1 电阻的等效电路

图2-2定性的给出了电阻的阻值与频率的关系。

图2-2 电阻的阻值与频率

我们试着分析电阻具有这样的特性的原因。当频率为0时(对应直流信号),电阻呈现出的阻值就是其自身的阻值;当频率提高时,电阻呈现出的阻值是自身的阻值加上电感呈现出的感抗;当频率进一步提高时,电阻自身的阻值加上电感的感抗已经相当的大,于是电阻表现出的阻值就是那个并联的电容的容抗,而且频率越高,容抗越小。

2.3. 微波频率下的电容

在射频电路中,电容是一种被广泛使用的元件,如旁路电容,级间耦合,谐振回路,滤波器等。和电阻一样,微波频率下电容的容抗特性也会发生很大的变化。

2.3.1. 电容的等效电路

我们知道,电容的材料决定着电容的特性参数,电容的等效电路如图2-3所示。C是电容自身的容值,Rp为并联的绝缘电阻,Rs是电容的热损耗,L是电容的引脚的电感。

图2-3 电容的等效电路

关于电容,我在这里介绍几个平时大家在选料是可能不会关注的参数。

图2-4定性的给出了电容在不同频率下的表现出的电抗特性。图中的纵轴为插入损耗(Insertion Loss),也就是由于电容的加入引起的损耗。

图2-4 电容在不同频率下的电抗特性

显然,在转折之前,电容表现出的是电容的特性,转折之后,电容表现出来的却是电感的特性。一般来说,大容量的电容会比小容量的电容表现出更多的电感特性。因此,在250MHz的频率下,一个0.1uF的旁路电容不一定比100pF的电容效果更好。换句话说,容抗的经典公式

似乎说明当频率一定时,电容的容量越大,容抗越小。但是在微波率下,结论是相反的。在微波频率下,一个0.1uF的电容会表现出比100pF电容更大的阻抗,这也是我们在设计电源电路时为什么要在大容量的电解电容;两端并联小容量的电容的原因,这些小容量的电容用于消除高频的噪声信号。

2.3.2. 电容的容量与温度特性

在CIS库中选料时,我们总会发现电容有一项参数为X7R或者X5R,NPO等,我特此搜寻相关资料,翻译过来,写在这一节中。

这类参数描述了电容采用的电介质材料类别,温度特性以及误差等参数,不同的值也对应着一定的电容容量的范围。具体来说,就是:

X7R常用于容量为3300pF~0.33uF的电容,这类电容适用于滤波,耦合等场合,电介质常数比较大,当温度从0°C变化为70°C时,电容容量的变化为±15%;

Y5P与Y5V常用于容量为150pF~2nF的电容,温度范围比较宽,随着温度变化,电容容量变化范围为±10%或者+22%/-82%。

对于其他的编码与温度特性的关系,大家可以参考表2-1。例如,X5R的意思就是该电容的正常工作温度为-55°C~+85°C,对应的电容容量变化为±15%。

表2-1 电容的温度与容量误差编码

2.4.1. 电感的等效电路

不难想象,导线的本身存在一定的电阻,相邻量个线圈之前存在一定的电容,于是,我们得到如图2-5所示的电感的等效电路。其中Rs为导线存在的电阻,L为电感自身的感值,C是等效电容。电感的电感量-频率曲线与电阻的阻抗-频率曲线颇有些相似,这与它们具有类似的等效电路有直接关系。读者可自行分析电感的频率特性曲线。

图2-5 电感的等效电路

2.4.2. 电感的Q值

电感的感抗与串联电阻Rs的比值称为电感的Q值,即Q=X/Rs与电容类似,Q值越大,则电感的质量越好。如果电感是一个理想电感,那么Q值应该是无限大,但是实际中不存在理想的电感,所以Q值无限大的电感是不存在的。

在低频情况下,电感的Q值非常大,因为这个时候Rs只是导线的直流电阻,这是一个很小的值。当频率升高时,电感的感抗X会变大,所以电感的Q值会随着频率的提高而增大(这个时候趋肤效应还不明显);但是,当频率提高到一定的程度的时候,趋肤效应就不可忽视了,这时串联电阻Rs会随着频率的提高而变大,同时串联电容C也开始发挥作用,从而导致Q值随着频率的提高而降低。图2-6给出了某公司的一款电感的Q值与频率的关系。

图2-6 某公司的电感的Q值与频率变化关系曲线

为了尽量增大电感的Q值,在制作电感时,我们通常可以采用以下的几种方法:

使用直径较大的导线,可以降低电感的直流阻抗;

将电感的线圈拉开,可以降低线圈之间的分布电容;

增大电感的磁导系数,这通常用磁芯来实现,如铁氧体磁芯。

其实,电感的手工制作,是射频工程师的必修课,但是这部分内容比较复杂,本文暂不进行讨论,感兴趣的读者可以查阅相关文献。

3 RF Debug经验分享

3.1. 某无线AP 2.4GHz Chain0 无输出功率

在一次对某无线AP(双频大功率11n无线AP)的测试 过程中,突然听到一声清脆悦耳的破裂声,随后看到一缕青烟缓缓的从板子上升起(可惜没看清具体是哪个位置),周围便迅速充满了令人不爽的焦臭味,VSA(Vector Signal Analyzer,矢量信号分析仪)上的功率也跌落至0dBm以下。稍微有点经验的人都可以得出一个结论:“有东西烧掉了”。

没有输出功率,可想而知,一定是Tx回路的某个器件损坏了,但是究竟是哪个呢?

首先采用目测法(所谓目测法就是直接用眼睛观察元器件的外观,查看是否有破裂或者烧焦的痕迹),结果没看出来。

然后采用“点测法”,这时候你可能会问:“什么是点测法呢?”点测法就是用探针或探棒直接检测待测点的信号状态,常用于时域信号检测,如示波器,但是由于Wi-Fi产品的工作频率较高,一般会通过频域进行信号检测,也很少使用点测法进行检测。

实践证明,点测法是一种确定RF问题所在的快速有效的手段。

说起点测法,不得不说说简易探针的制作。取一条SMA Cable(如图3-1所示),将其一端的SMA连接器去掉(不可以将两端的都去掉),剥去长度1~2cm屏蔽层,使其芯线露出。这样,一段普通的SMA Cable就此华丽转身,升级为点测探针,成为一种检测利器,也成为了RF工程师的好助手。

3.2. 输出功率过大

现象:输出功率超级大,星座图一片模糊,无法解调。

这是一个稍显复杂的问题。

我们知道,Atheros的方案都会有输出功率的控制部分,也就是让Target Power和实际功率值相一致,这是如何实现的呢?我们将AP96的2.4GHz PA部份电路取出进行研究,如图3-2所示。

图3-2 2.4GHz PA电路

在图3-2中,U27及其外围电路组成了功率放大器,经过C208和R263送至后续的电路。图中的PC1是一颗印制定向耦合器,其3,4两脚的电压随着输出功率的增大而增大,L18,L19,D1,C217和R248组成了半波整流电路,将定向耦合器感应到的电压变为直流电信号,并送至Transceiver检测,也就是AR9223_PDET_0这个网络。这样,Transceiver就可以随时知道当前的输出功率,功率与电压值的关系是在Calibrate的过程中建立的。

板子经过Calibrate并Load EEPROM之后,我们用ART进行Continue Tx,这时,板子会按照我们设定的Target Power打出信号,Transceiver会提高自身的输出功率直至与Calibrate过程中记录的对应的那个电压值(AR9223_PDET_0)一致。

这时我们回到一开始的问题“输出功率超级大,星座图一片模糊,无法解调”,怎么回事?肯定是Transceiver无法得到正确的那个电压值,所以只能一直提高自身的输出功率直至PA的输出功率达到饱和。检查L19,L18,D1,C217,R248,发现D1已开路,换一颗新的二极管,恢复正常。

这里需要指出的是,采用定向耦合器进行输出功率控制是Atheros特有的一种方法,Broadcom和Ralink中至今还未看到采用这种方法的。另外,PA的本身一般都会内置功率检测单元,并通过一个引脚出来,通常成为V_DET。

3.3. 某无线网卡静态发热严重

现象:某无线网卡 上电后,不做任何操作,四颗PA就发出很大的热量,PA的表面温度很高,很烫手。

第一判断就是PA并不是处于真正的“静态”,它们正在偷偷地工作!那么,如何验证呢?拿来PA(SKY65137-11)的Demo板,用Power Supply供电,以便观察其消耗的电流。上电,发现消耗的电流几乎为零,并不会出现发热的现象,与该无线网卡的情况不一样。研读SKY65137-11的Datasheet,一个关键的引脚PA_EN引起了我的注意,这个引脚就是PA的使能引脚。在上电情况下,将此引脚拉高至3.3V,发现5V消耗的电流剧增,随之散发出大量的热,PA的表面温度立刻上升。将PA_EN与3.3V断开,5V消耗的电流随之下降,这时,用手触碰PA_EN引脚,发现5V消耗的电流在发生跳动,这说明人体感应到的微弱电信号足以使PA处于“Enable”状态,同时说明,PA_EN是一个很敏感的引脚,很微弱的信号就足以触发。

分析该无线网卡的SKY65137-11单元电路,如图3-3所示(不包括Level Shift)。

图3-3 SKY65137-11单元电路

很容易发现,SKY65137-11的PA_EN这个引脚是通过一个Level Shift电路直接与AR9220的控制引脚进行连接,这样,AR9220控制引脚的微弱扰动就可以触发PA,所以会导致静态情况下PA发热。

解决办法:在PA_EN引脚处用一颗10K电阻下拉倒地,使常态下PA处于关闭状态。

通过上述办法,解决了PA的发热问题

3.4. 某无线网卡 Calibrate 不准

现象:该无线网卡经Calibrate之后,实际输出功率与Target Power不一致。

首先经过排查,确定不是Cable Loss与ART的设定问题。该无线网卡的RF部份是我们自主设计的,有太多不确定的因素,这里不进行深入的分析。在3.2中已经讨论过,Atheros的方案通过检测PA的输出功率对应的电压值来实现输出功率的稳定;静态情况下,若PA无输出功率,则对应的电压值为零。通过检测,发现SKY65135-21(2.4GHz PA)在静态下输出的V-Detect并不是零,而是零点几伏的电压值,这可能是PA自身的问题造成的,也正是这个原因,导致了该无线网卡的Calibrate不准的问题。我们都知道二极管的单向导电特性,为了防止该无线网卡 的2.4GHz与5GH频段在Calibrate过程中相互影响,可以通过二极管将其分开。在该无线网卡后续的版本中,我们就是采用了这种方式,可以很好的解决Calibrate不准的问题。

3.5. 某无线AP无输出信号

现象:ART运行一切正常,用VSA观察,无任何输出信号。

回忆3.1中讲解的内容,我们提到了点测法,个人认为,点测法是解决类似这种问题的最快手段,在使用ART进行Continue Tx的情况下,使用探针依次检测Transceiver输出端,PA输入端,PA输出端,低通滤波器输出端,T/R Switch输入端及T/R Switch输出端,一般来说,检测这些点已经足够了。

按照上述的方法,我们依次检测Tx回路的各点(以2.4GHz 链路0为例),如图3-4所示。

图3-4 2.4GHz 0链路检测点

在实际的检测过程中,发现在T/R Switch输入端有信号,也即C379处有正常的RF信号,但是在T/R Switch输出端无信号,查阅T/R Switch uPG2179的Datasheet,发现,此时的控制信号与预想的不符,细节部分读者请参阅uPG2179 Datasheet与AR9280(此项目的Transceiver)的参考设计。

(本文转自网络)

相关问答

无线网卡是怎么接受路由器的信号的?-180****4885的回答-...

网卡里一个概念叫descripter,它是DMA和CPU交换控制的一个固定结构链表。在初始化的时候,申请一定数目的和descripter的结构一样大小的内存给网卡。...

用ROS,做无线路由器,最廉价的无线网卡是哪款-ZOL问答

列出了ROS3.0版本所支持的所有网卡型号就我目前所知,最便宜的是DlinkDWL-G650,大约35元,当然功率不是很大,如果做无线路由,只能一个房间内的机器可以连接...

台式机的WIFI有兰牙功能吗?能当网卡吗-ZOL问答

直接购买usb蓝牙适配器和usbWi-Fi网卡即可京东有售有用(0)回复Jay456321...将现在插在电脑上的网线插在无线路由的wan接口上,然后从路由的其他接口,如标注...

无线网卡是不是我们所说的wifi

[最佳回答]无线网卡不是我们所说的wifi。区别如下。1.WIFI这个只是一种无线宽带上网的标准,就像手机标准有GSM,WCDMA的标准一样。2.无线网卡,这个只是上...

笔记本只有一根天线,是接无线网卡MAIN的接口还是接AUX?-ZOL问答

笔记本无线网卡的main与aux都是预留接天线用的,接上天线后无线的信号会更加强,对于无线上网有很大的好处。天线接上去,只是让系统增加无线信号,不会识别到新...

蓝牙耳机上:FCCID和CMIITID是什么意思?-ZOL问答

FCCID为无线产品出口美国的强制性要求需要申请ID注册,周期20天左右,CMIITID中国无线电产品型号核准RTA启用新的CMIITID标识方法FCCID、IC、SPS、TA、WFM...

这是我电脑无线网卡位置,问一下上面两根线是干什么的,肿么接...

这两根线是无线网卡带的吗?一般无线网卡会有两个或3个插座,用图中这种插头插上就行了天线,增强信号的一般来说,那两根细长的是馈电线和电源/控制线路。将它...

电脑突然每次都要重装网卡驱动才能投入使用无线网卡-ZOL问答

您的问题是由于计算机未安装无线网卡驱动引起,建议您通过以下网页链接下载对应XP操作系统的无线网卡驱动进行安装:http://h10025.www1.hp.com/ewfrf/wc/documen...

LB-LINK802.11N无线网卡的驱动是哪个?-ZOL问答

告诉我产品型号或硬件ID我发你驱动链接LB-LINK无线网卡的驱动一般去他们官网...回复dsrfkwupfaxn可能是驱动问题。下载“驱动人生”检测一下。或打开...

windows7旗舰版怎么找出无线网卡开关啊?-ZOL问答

无线网卡开关,为分两类:一、硬件开关1、一般是在笔记本电脑本身,有一个很小的开关;2、或者是Fn+Fx组合键(Fx为F1-F12功能键),上面会有一个无线网的标志;二...